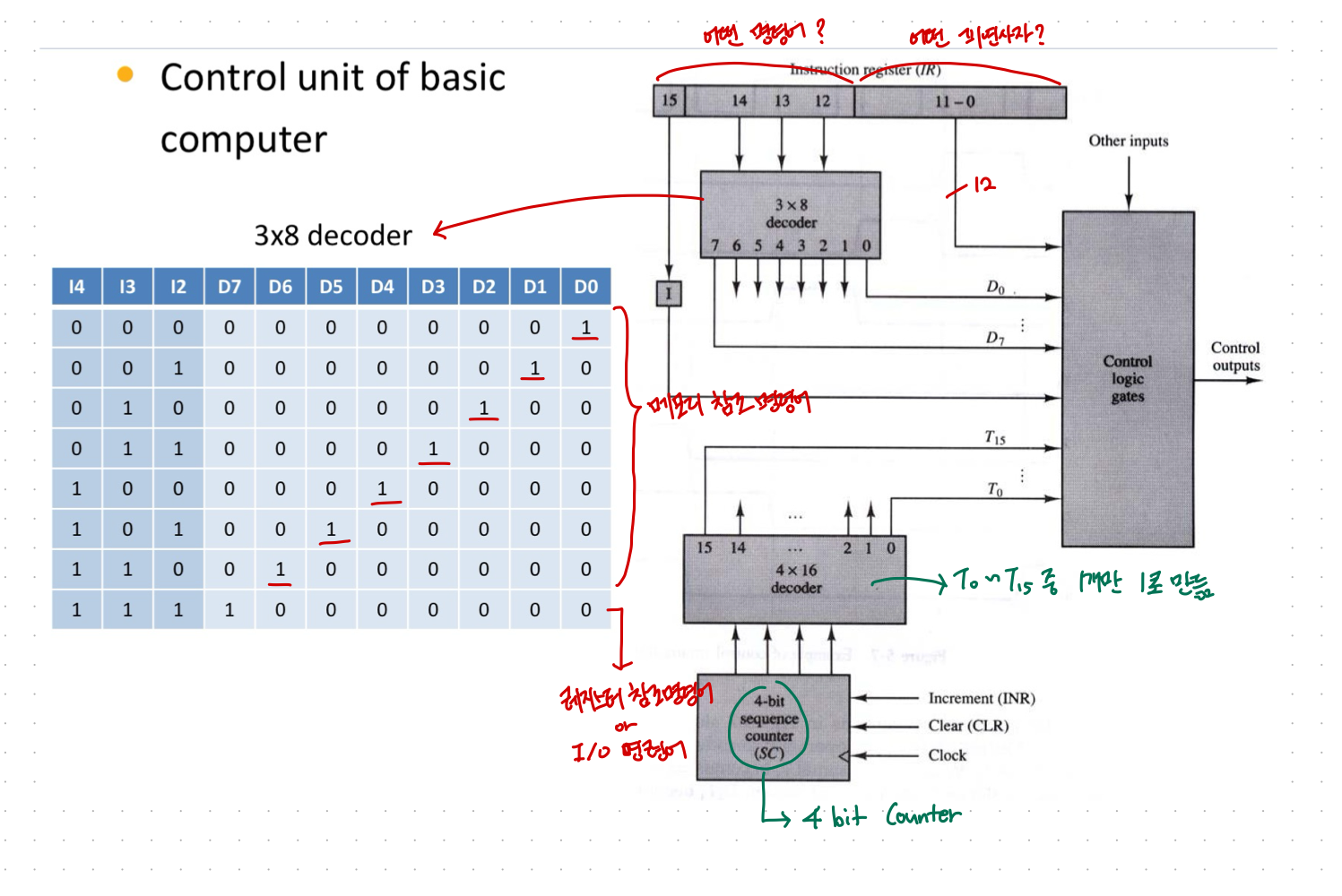

IR(Instruction Register)

: 현재 CPU가 실행할 명령어를 저장한다.

3x8 decoder + I

: Opcode, 메모리 참조 명령어를 사용할지, 레지스터 참조 명령어를 참조할지, I / O 명령어를 사용할지를 결정

4x16 decoder

: 명령어를 순차적으로 실행하기 위해 클럭과 연결된 시퀀스 카운터를 사용해서 제어 신호를 생성한다.

Control Logic Gates

: 디코더에서 나온 신호를 기반으로 제어 논리가 구성되어 CPU 내부 작업 흐름을 제어하는 신호를 생성한다.

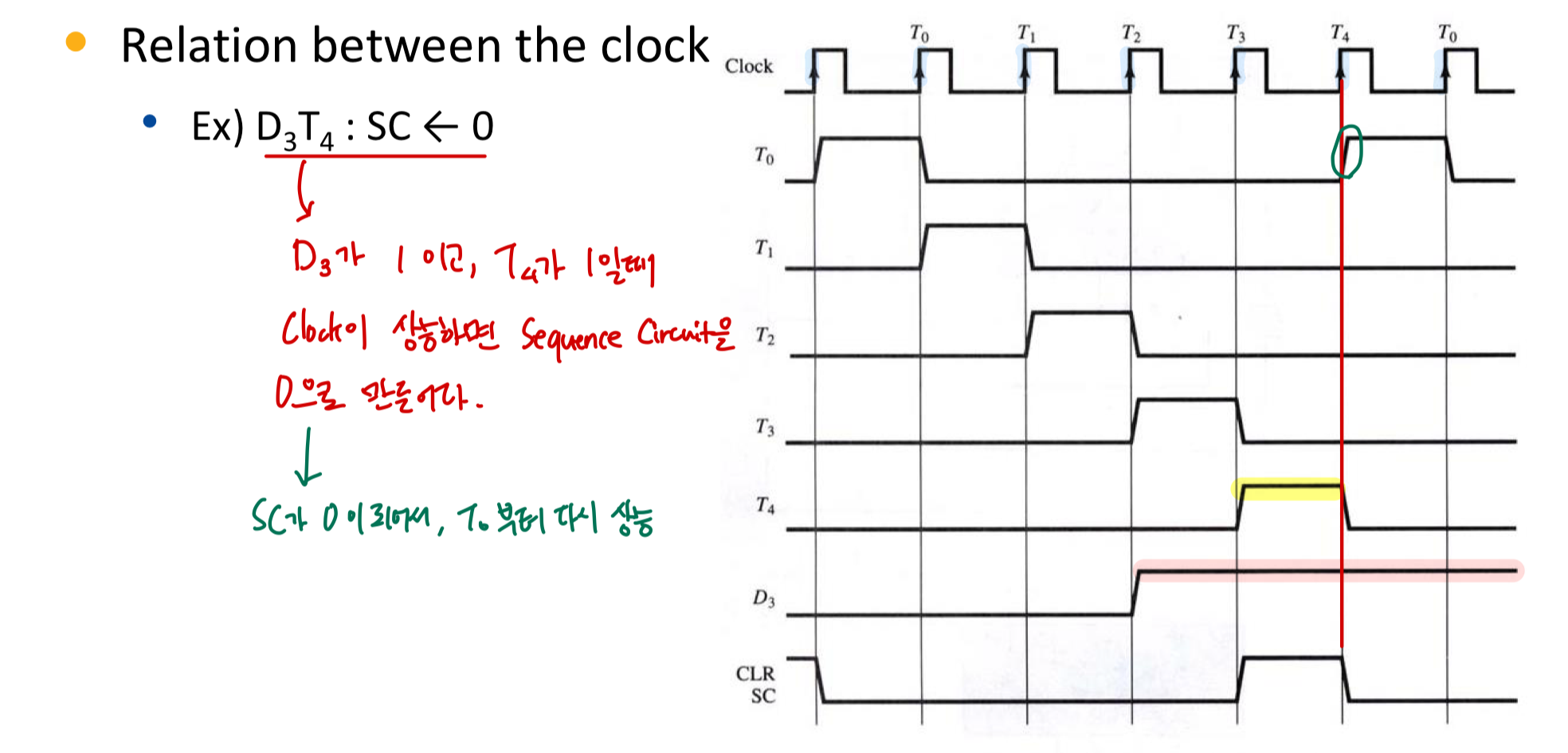

Timing

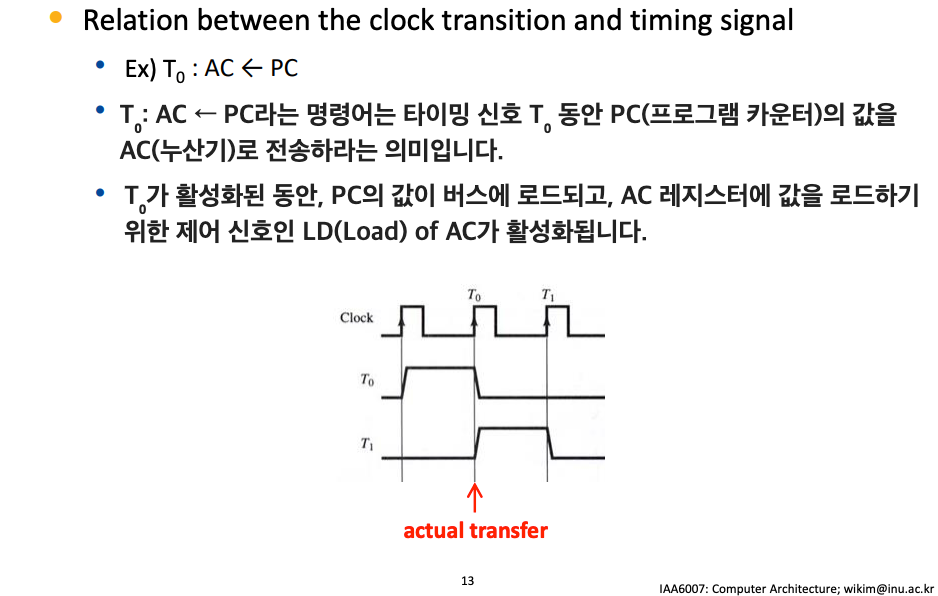

클럭 신호(Clock Signal)와 타이밍 신호(Timing Signal) 간의 관계

여기서 중요한 것은 실제 데이터 전송은 클럭이 상승하는 순간 발생한다. 클럭의 신호는 주기적으로 변경되는데, T₀ 단계에서는 PC의 값이 bus에 로드되고, 클럭이 상승하는 순간 PC 값이 AC에 로드된다.

'2학년 2학기 > 컴퓨터 구조' 카테고리의 다른 글

| 5.6 Memory reference instructions (0) | 2024.10.27 |

|---|---|

| 5.5 Instruction cycle + Register reference instruction (1) | 2024.10.27 |

| 5.3 Computer Instructions (0) | 2024.10.27 |

| 5.2 Computer registers (0) | 2024.10.27 |

| 5.1 Instruction codes (0) | 2024.10.27 |