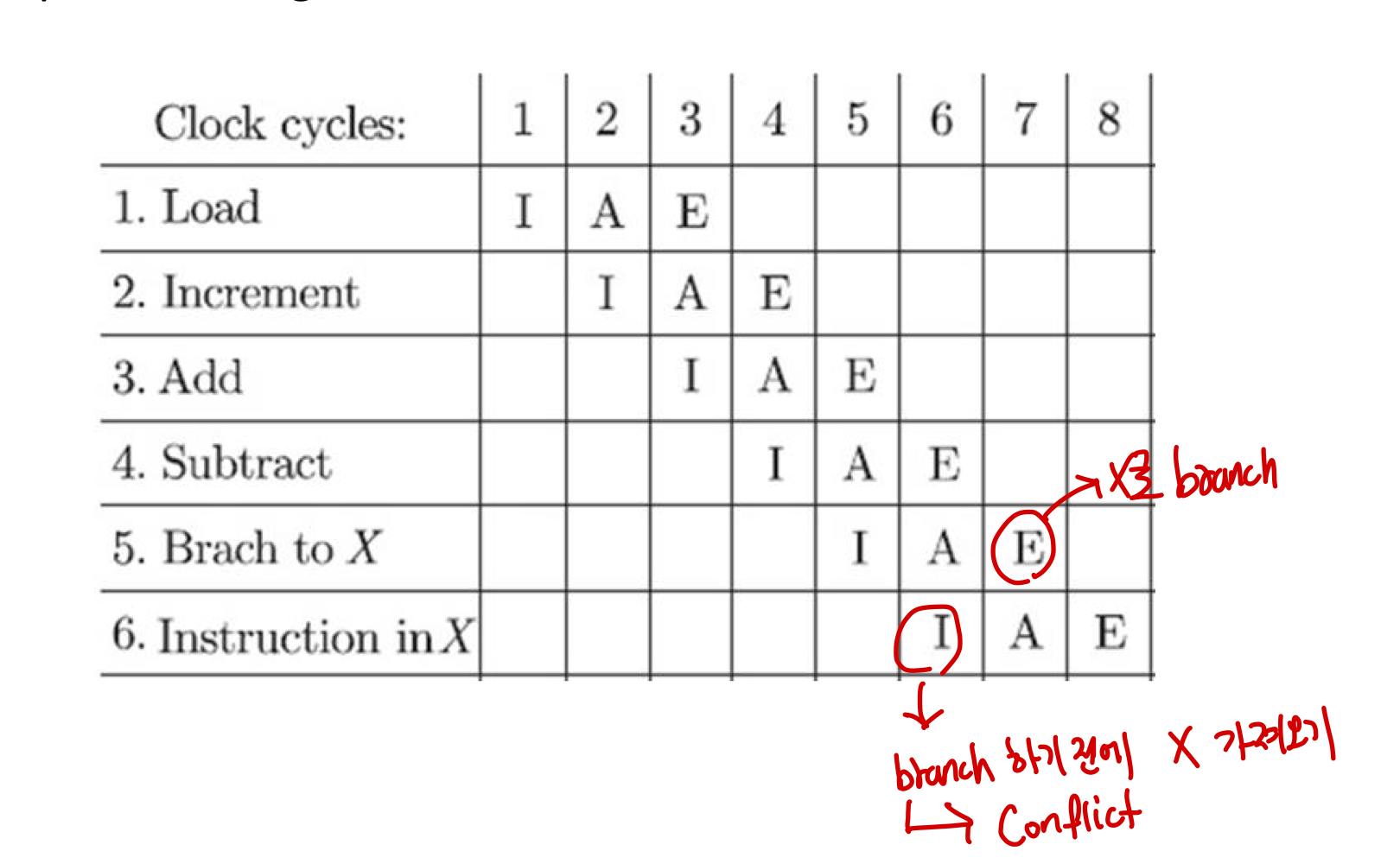

RISC 아키텍쳐에서는 명령어를 3단계로 나누어 처리한다. 각 단계는 병렬로 실행되며, Pipelining을 통해 처리 속도를 높인다.

- I : Instruction Fetch (명령어 가져오기)

- A : Decode, Read Registers (명령어 해독 및 레지스터 읽기)

- E : Execute (실행)

1. Data Manipulation Instructions

: 데이터 조작 명령(예: 산술 연산, 논리 연산)를 처리한다.

- I : Instruction Fetch (명령어를 메모리에서 가져오기)

- A : Decode, ALU operations

- 명령어 해독 및 실행할 연산 결정

- 필요한 레지스터 값을 읽기

- ALU를 통해 산술 또는 필요한 레지스터 값을 읽는다.

- E : Write a register (연산 결과를 레지스터에 저장)

2. Data Transfer Instructions (Load/Store)

: 프로그램 흐름을 제어하는 명령어(예를 들면, Branch, Jump)를 처리한다.

- I : Instruction Fetch (명령어 가져오기)

- A : Decode, Evaluate effective address (명령어를 해독하고 메모리 주소 계산 필요한 레지스터 값이나 오프셋을 확인)

- E : Register-to-memory or Memory-to-register(레지스터 값을 메모리에 저장(Store)하거나, 메모리 값을 레지스터로 가져옴(Load))

3. Program Control Instructions

: 프로그램 흐름을 제어하는 명령어(예를 들면, Branch, Jump)를 처리한다.

- I : Instruction Fetch (명령어 가져오기)

- A : Decode, Evaluate branch address (명령어 해독 및 branch 주소 계산)

- E : Write registr / PC (계산된 branch 주소를 PC에 저장)

Delayed Load로 Conflict 해결

Branch시 발생하는 Conflict를 2가지 방법으로 해결하기

'2학년 2학기 > 컴퓨터 구조' 카테고리의 다른 글

| 9.4 Instruction pipeline (0) | 2024.11.24 |

|---|---|

| 9.2 Pipelining (0) | 2024.11.24 |

| 9.1 Parallel processing(Instruction Level Parallelism) (0) | 2024.11.24 |

| 8.8 Reduced Instruction Set Computer (RISC) (0) | 2024.11.17 |

| 8.7 Program control (0) | 2024.11.17 |